《The Hardware Knowledge that Every Programmer Should Know》

理解硬件细节是程序性能优化的关键,单靠算法和代码优化无法突破瓶颈。以下几点洞见,助你构建更高效的程序:

• 缓存友好访问:按行主序(row-major)遍历二维数组比列主序快约10倍,因缓存行连续加载数据,减少缓存未命中,提升访问速度。随机遍历则打破预取机制,性能进一步下降。🧠

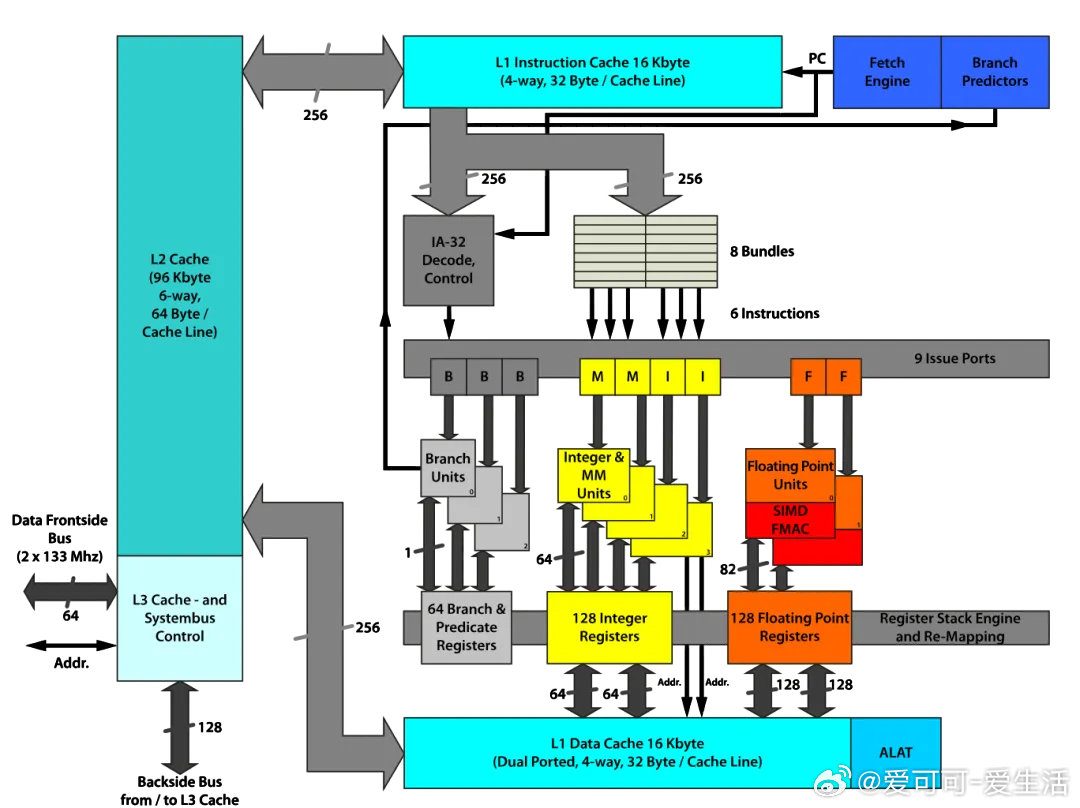

• 缓存组相联性(Cache Associativity):当访问步长(step)为2的幂时,频繁发生缓存冲突,导致性能骤降。现代CPU如AMD Ryzen采用8路组相联,合理设计内存访问模式避免热点数据映射到同一缓存组至关重要。

• 伪共享(False Sharing):多线程访问相邻但不同变量时,若变量共占一个缓存行,会相互干扰,导致性能大幅下降。通过内存对齐(如64字节对齐),将变量分散到不同缓存行,可近乎翻倍提升效率。

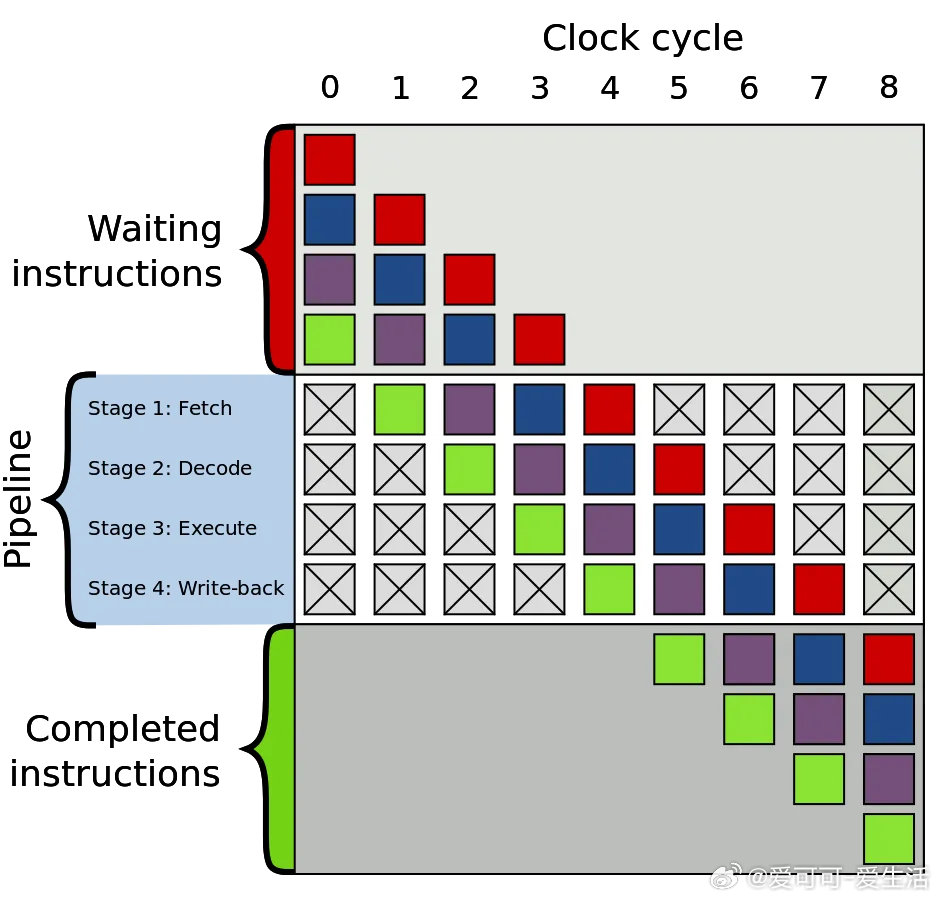

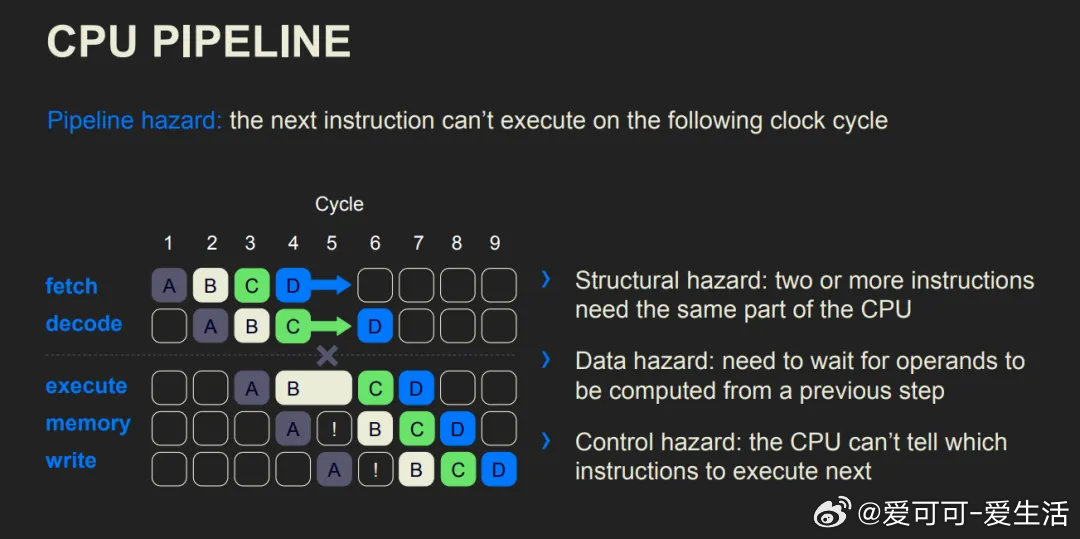

• 流水线与分支预测:CPU流水线需提前加载指令,分支预测准确率高达99%,但预测失败代价巨大。数据结构排序优化能减少分支失败,提升约2.7倍性能。

• 数据依赖与指令级并行:循环内部迭代间依赖阻碍指令并行和向量化优化,消除数据依赖可使性能提升近3倍,编译器更易生成高效SIMD代码。

三点启发:

1. 性能优化不仅靠代码逻辑,理解硬件缓存架构与访问模式是根本。

2. 并发编程时,避免伪共享和合理内存布局对多核性能影响极大。

3. 优化分支和数据依赖结构,提升流水线效率,才能真正释放CPU潜力。

深入理解这些硬件机制,能帮助程序员写出更高效、可持续优化的代码。

🔗 needoneapp.medium.com/the-hardware-knowledge-that-every-programmer-should-know-f62cf4ba8bdc

程序性能 缓存优化 多线程 CPU架构 高性能编程