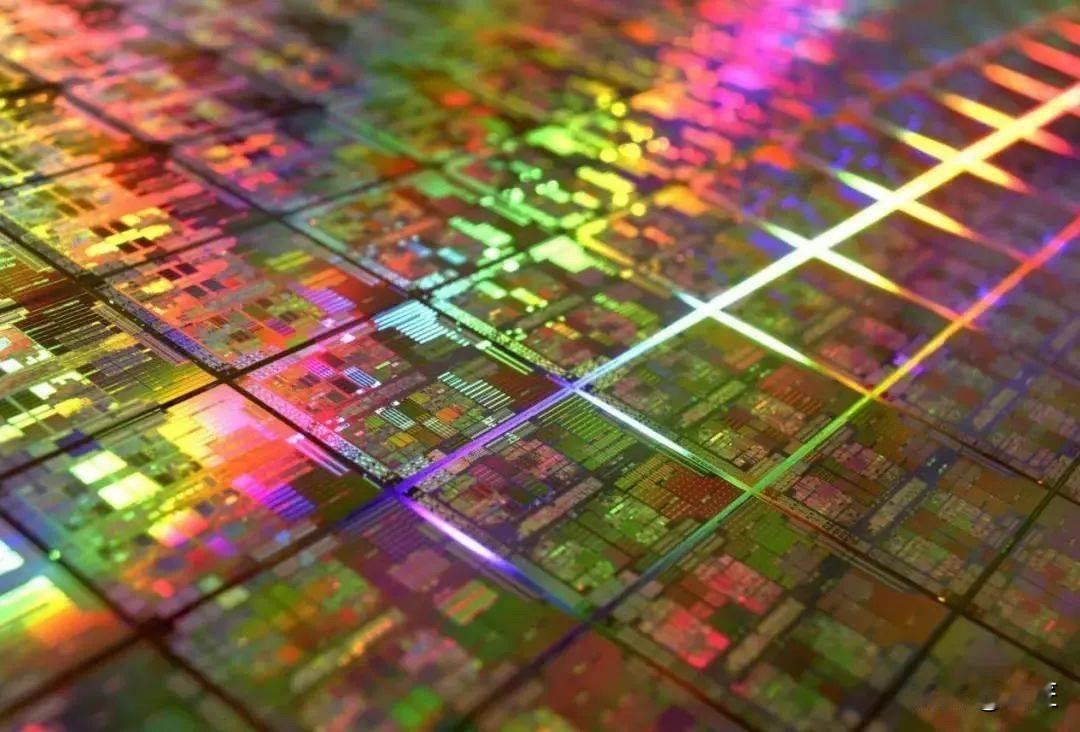

台积电2nm GAA纳米片晶体管:一次晶体管结构的革命。工艺突破,良率已达90%。 台积电2nm工艺首次采用全环绕栅极(GAA)纳米片晶体管,实现栅极四面环绕沟道,相比FinFET的3面包裹,静电控制能力提升40%,漏电率降低50%。 传统的FinFET(鳍式场效应晶体管)采用3D鳍片结构,栅极仅包裹沟道的三个面。 当制程微缩至5nm以下时,这种结构面临严重的短沟道效应和漏电问题。 GAA(Gate-All-Around)纳米片晶体管通过以下创新解决这些问题: 四面环绕栅极:栅极完全包裹由水平堆叠纳米片构成的沟道,实现360度电场控制。 纳米片堆叠:采用多层超薄纳米片垂直堆叠,增加有效沟道宽度而不增加面积。 精准尺寸控制:纳米片厚度可精确控制在5nm以下,实现原子级精度。 关键工艺突破: 纳米片形成:采用选择性蚀刻技术精确控制纳米片厚度,误差小于0.5nm。 栅极堆叠:开发新型ALD(原子层沉积)工艺,实现均匀栅极包裹。 应变工程:在纳米片中引入应变硅技术,提升载流子迁移率。 电源网络:集成超高性能MIM电容器,电容密度提升2倍。 良率进展: 2025年8月,台积电2nm工艺良率已达90%(SRAM测试),为大规模量产奠定基础。 预计2026年成熟良率将达到75-80%。 台积电 纳米芯片 半导体EDA 二维环栅晶体管 5nm芯片技术