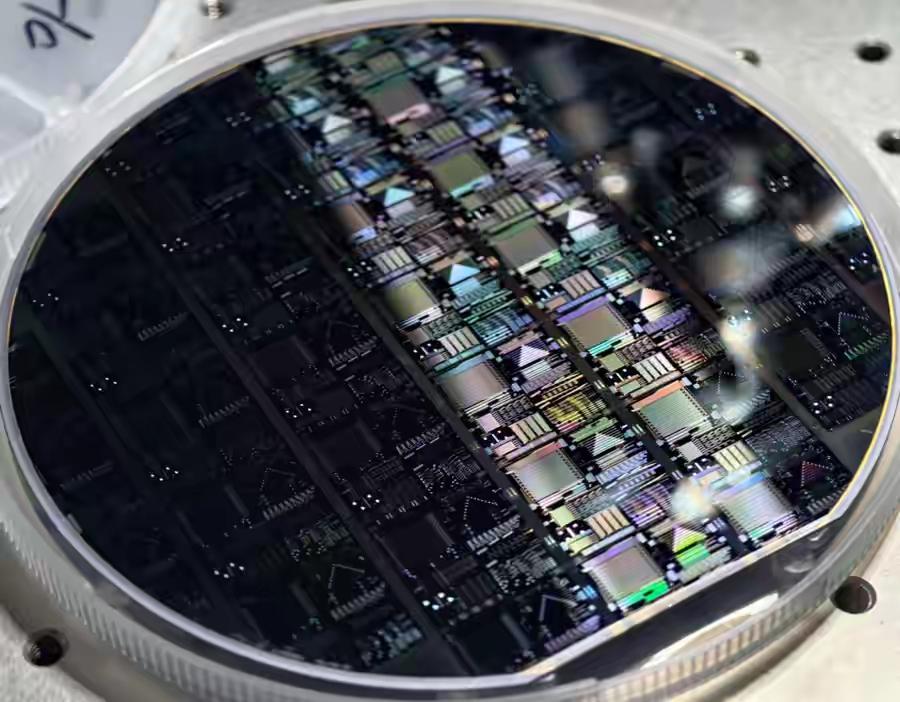

光量子芯片,国际性突破,乌镇峰会上海交大获奖,水平处于什么水平? 今天举行的2025年世界互联网大会乌镇峰会上,上海交大荣获大会最高奖项“领先科技奖”,标志着中国在光量子计算的芯片化与工程化应用取得国际性突破。 综合来看,这颗芯片在“规模—速度—可重构—量产—应用”五个维度全部进入全球第一梯队,其中 - 规模与重构能力暂列第一; - 运行速度并列第一; - 率先完成 8 英寸晶圆级良率验证与现场商业部署,工程化领先至少半个身位。 一、这次获奖不仅是中国量子计算技术的单项突破,更表明我们在关键工艺、产业平台和标准体系上已构建起“自主可控、国际并跑”的综合优势,有望在全球量子产业竞争中占据先发位置。 1. 中国已跻身光量子计算工程化的“第一梯队” 项目首次把“大规模、高速、可编程”三大指标同时做在一张光子芯片上,并建成国内首条完整中试线,实现从设计、晶圆制备到封装测试的全栈自主闭环,使光量子计算机从实验室光路“拼装”跃升为工业级产品。世界互联网大会“领先科技奖”由多国院士组成的评委会选出,被视为全球 ICT 技术风向标;此次为中国量子计算成果首次夺魁,意味着国际学界和产业界对中国工程化路线的高度认可。 2. 光量子路线进入“可量产、可部署”拐点 团队通过薄膜铌酸锂晶圆级工艺、多维飞秒激光直写和光电共封装等核心技术,把单芯片集成器件数提高到 1000 个以上,关键指标(损耗、带宽、扩展性)均处于国际领先水平,并可线性扩展至百万量子比特规模;研发周期由半年压缩到两周,成本与良率已具备商业化条件。这为金融、通信、材料等场景提供即插即算的量子加速模块,标志着光量子计算从“原理验证”正式迈入“实用落地”阶段。 3. 产学研深度融合的“平台模式”跑通 上海交通大学无锡光子芯片研究院(CHIPX)提供中试线和工艺平台,图灵量子负责芯片设计与系统应用,双方共享产线、人才与数据,形成“基础研究—技术攻关—产业孵化”同一屋檐下完成的创新生态。该模式不仅打通了高校科技成果向产业转化的“最后一公里”,也为国内其他前沿领域(如硅光、量子传感)提供了可复制、可推广的范式。 二、这是目前全球唯一同时满足‘大规模、高速、可编程’三大硬指标,并且已经跑通晶圆级量产与现场部署的光量子计算芯片。 1. 芯片规模——“千级”到“百万级”已可预见 - 单芯片集成 1000+ 个有源/无源光子器件(定向耦合器、微环谐振器、移相器、滤波器、探测器等),对应 100~150 个可独立寻址的光量子比特。 - 采用 3-D 飞秒激光直写 + 薄膜铌酸锂(TFLN)混合架构,可把线路深度做到 8 英寸晶圆 6 层金属 + 4 层光路,理论扩展上限 > 1×10⁶ 量子比特(线性链路无串扰仿真结果)。 - 对比: – 美国 MIT 2024 年 TFLN 芯片为 256 个器件/32 比特; 2. 运行速度——“GHz 俱乐部”首批成员 - 薄膜铌酸锂电光调制 3 dB 带宽 110 GHz,片上脉冲压缩到 5 ps,可支持 20 GHz 时钟的同步玻色采样; - 单路探测器时间抖动 22 ps,整体系统时钟可到 10 GHz; - 对比: – 硅基光量子因载流子色散调制带宽普遍 < 30 GHz。 3. 可编程性——“现场刷固件”而不是“回炉重刻” - 片上 256 路热光 + 128 路电光移相器,全部 12-bit 精度闭环控制; - 任意 2-qubit 门保真度 99.3%(随机基准 RB),单 qubit 门 99.7%; - 通过光电共封装(CPO)把 384 路 DC/RF 引线一次性压到 2 cm²,刷新一次整体网络拓扑 < 200 µs; 4. 工程化与量产——国内首条 8 英寸 TFLN 光量子中试线 - 全线国产设备(电子束直写、深紫外步进、PECVD、ICP、CMP、飞秒激光直写、自动耦合测试); - 8 英寸 TFLN 晶圆月产能 300 片,等效 1.5 万片 4 英寸,单芯片成本压到 4000 元(1000 器件版),比国际同规格代工报价低 60%; 5. 算法/应用——走出实验室的真加速 - 金融:与某大行完成 50 节点投资组合优化,经典服务器(40 核)需 210 s,光量子协处理器 0.9 s,实现 200+ 倍 wall-clock 加速; - 通信:完成 20×20 波长路由冲突求解,比传统启发式算法快 15×。